# Xtium2-CLHS PX8<sup>™</sup>

User's Manual Edition 1.10

945 East 11th Avenue Tampa, FL 33605

Phone: (813) 984-0125

Contact: Sales@ pyramidimaging.com

https://pyramidimaging.com

sensors | cameras | frame grabbers | processors | software | vision solutions

P/N: OC-A8SM-PX8U0

Revision: 02

www.teledynedalsa.com

#### **NOTICE**

© 2018-2019 Teledyne DALSA, Inc. All rights reserved.

This document shall not be reproduced nor transmitted in any form or by any means, either electronic or mechanical, without the express written permission of TELEDYNE DALSA. Every effort is made to ensure the information in this manual is accurate and reliable. Use of the products described herein is understood to be at the user's risk. TELEDYNE DALSA assumes no liability whatsoever for the use of the products detailed in this document and reserves the right to make changes in specifications at any time and without notice.

$\label{lem:microsoft} \begin{tabular}{ll} Microsoft @ is a registered trademark; Windows @ 7, Windows @ 8, Windows @ 10 are trademarks of Microsoft Corporation. \end{tabular}$

All other trademarks or intellectual property mentioned herein belongs to their respective owners.

Edition 1.10, Revision 02 released April 30, 2019

Document Number: OC-A8SM-PX8U0

Printed in Canada

#### About Teledyne DALSA

Teledyne DALSA is an international high performance semiconductor and electronics company that designs, develops, manufactures, and markets digital imaging products and solutions, in addition to providing wafer foundry services.

Teledyne DALSA Digital Imaging offers the widest range of machine vision components in the world. From industry-leading image sensors through powerful and sophisticated cameras, frame grabbers, vision processors and software to easy-to-use vision appliances and custom vision modules.

# Contents

| OVERVIEW                                                              | 6  |

|-----------------------------------------------------------------------|----|

| PRODUCT PART NUMBERS                                                  | 6  |

| ABOUT THE XTIUM2-CLHS PX8 FRAME GRABBER                               | 7  |

| Series Key Features                                                   | 7  |

| User Programmable Configurations                                      | 7  |

| ACUPlus: Acquisition Control Unit                                     | 7  |

| DTE: Intelligent Data Transfer Engine                                 | 8  |

| PCI Express x8 Gen3 Interface                                         | 8  |

| Advanced Controls Overview                                            | 8  |

| DEVELOPMENT SOFTWARE OVERVIEW                                         | 9  |

| Sapera++ LT Library                                                   | 9  |

| Sapera Processing Library                                             | 9  |

| QUICK START SETUP & INSTALLATION                                      | 10 |

| INSTALLING XTIUM2-CLHS PX8                                            | 14 |

| Warning! (Grounding Instructions)                                     | 14 |

| INSTALLATION                                                          | 14 |

| Hardware Installation                                                 | 14 |

| Multi-board Data Forwarding Hardware Setup                            | 14 |

| Multi-board Sync & I/O Setup                                          | 14 |

| Sapera LT Library & Xtium2-CLHS PX8 Driver Installation               | 15 |

| Teledyne DALSA Device Drivers                                         | 15 |

| Installation Procedure                                                | 15 |

| Xtium2-CLHS PX8 Firmware Loader                                       | 16 |

| Firmware Update: Automatic Mode                                       | 16 |

| Firmware Update: Manual Mode                                          | 16 |

| Executing the Firmware Loader from the Start Menu                     | 18 |

| Upgrading Sapera or Board Driver                                      | 19 |

| Board Driver Upgrade Only                                             | 19 |

| Upgrading both Sapera and Board Driver                                | 19 |

| DISPLAYING XTIUM2-CLHS PX8 BOARD INFORMATION                          | 20 |

| Device Manager - Board Viewer                                         | 20 |

| Information Field Description                                         | 21 |

| Changing Device Settings                                              | 23 |

| Device Information Report                                             | 23 |

| CONFIGURING SAPERA                                                    | 24 |

| Viewing Installed Sapera Servers                                      | 24 |

| Increasing Contiguous Memory for Sapera Resources                     | 24 |

| Contiguous Memory for Sapera Messaging                                | 25 |

| CAMEXPERT QUICK START                                                 | 26 |

| INTERFACING CLHS CAMERAS WITH CAMEXPERT                               | 26 |

| Sapera Camera Configuration Files                                     | 28 |

| Camera Types & Files                                                  | 28 |

| Overview of Sapera Acquisition Parameter Files (*.ccf or *.cca/*.cvi) | 28 |

| Saving a Camera File                                                  | 29 |

| Camera Interfacing Check List                                         | 29 |

| USING CAMEXPERT WITH XTIUM2-CLHS PX8                                  | 30 |

| Basic Timing Category                                                 | 31 |

| Parameter Descriptions                                                | 31 |

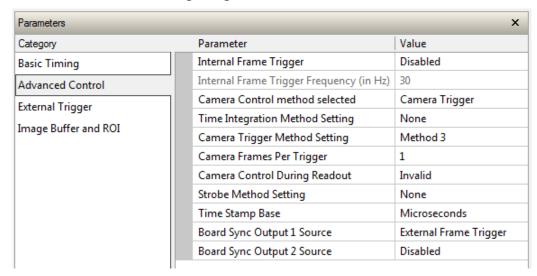

| Advanced Control Category                                             | 33 |

| Parameter Descriptions                                                                   | 33        |

|------------------------------------------------------------------------------------------|-----------|

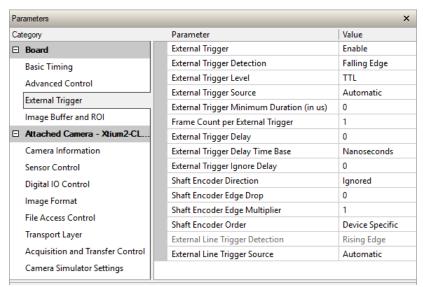

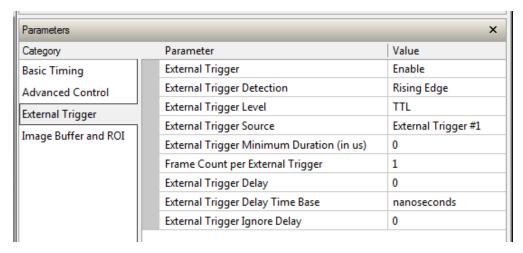

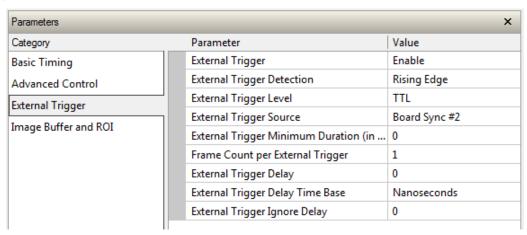

| External Trigger Category                                                                | 35        |

| Parameter Descriptions                                                                   | 35        |

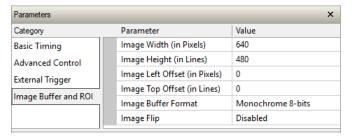

| Image Buffer and ROI Category                                                            | 37        |

| Parameter Descriptions                                                                   | 37        |

| SAPERA DEMO APPLICATIONS                                                                 | 39        |

| Grab Demo Overview                                                                       | 39        |

| Grab Demo Workspace Details                                                              | 39        |

| Using the Grab Demo                                                                      | 40        |

| XTI UM2-CLHS PX8 REFERENCE                                                               | 41        |

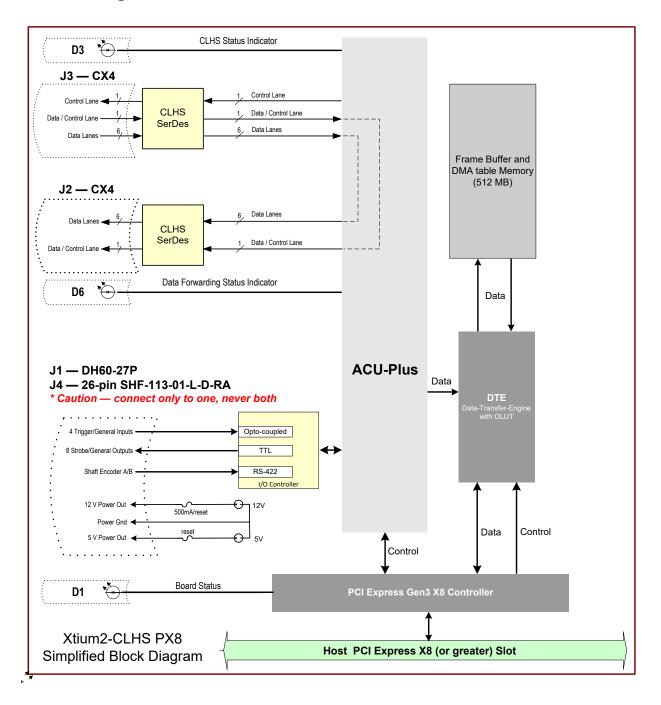

| BLOCK DIAGRAM                                                                            | 4 I<br>41 |

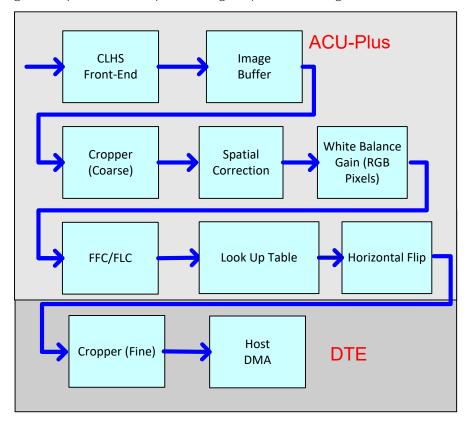

| XTIUM2-CLHS FLOW DIAGRAM                                                                 | 42        |

| CLHS CAMERA IMPLEMENTATION                                                               | 43        |

| LINE TRIGGER SOURCE SELECTION FOR LINE SCAN APPLICATIONS                                 | 43        |

| CORACQ_PRM_EXT_LINE_TRIGGER_SOURCE - Parameter Values Special                            |           |

| the Xtium2-CLHS PX8                                                                      | 44        |

| SHAFT ENCODER INTERFACE TIMING                                                           | 44        |

| VIRTUAL FRAME TRIGGER FOR LINE SCAN CAMERAS                                              | 46        |

|                                                                                          | 46        |

| Virtual Frame Trigger Timing Diagram Synchronization Signals for a 10 Line Virtual Frame | 40<br>47  |

| Synchronization Signals for a 10 Line Virtual Frame                                      | 47        |

| Synchronization Signals for Fixed Frame Length Acquisition                               | 47        |

| Synchronization Signals for Variable Frame Length Acquisition Sapera Acquisition Methods | 50        |

| TRIGGER TO IMAGE RELIABILITY                                                             | 50        |

| Supported Events and Transfer Methods                                                    | 50<br>50  |

| Acquisition Events                                                                       | 50        |

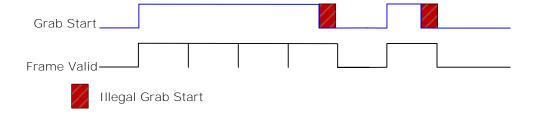

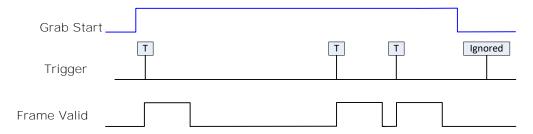

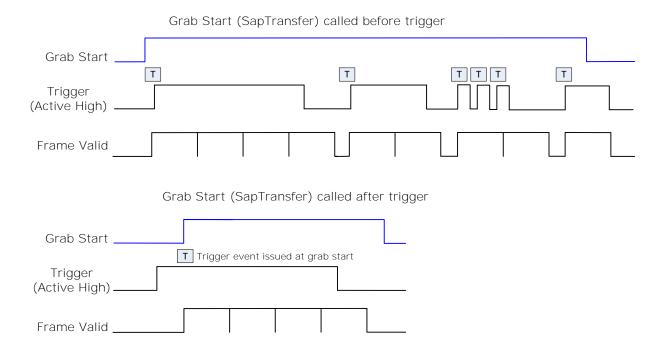

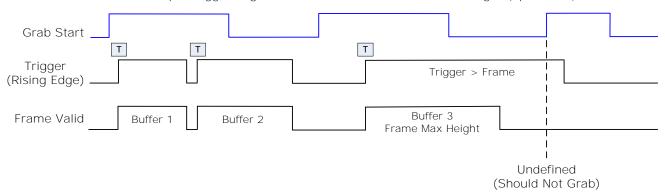

| Trigger Signal Validity                                                                  | 52        |

| Supported Transfer Cycling Methods                                                       | 52        |

| Output LUT Availability                                                                  | 52<br>54  |

| METADATA: THEORY OF OPERATION                                                            | 55        |

| Metadata Data Structure                                                                  | 55<br>55  |

| FLAT FIELD CORRECTION: THEORY OF OPERATION                                               | 56        |

| Flat Field Correction Lists                                                              | 56        |

| Flat Field Correction Sets                                                               | 57        |

| Xtium2-CLHS PX8 specific limitations                                                     | 57        |

| Programming the sets                                                                     | 57<br>57  |

| XTIUM2-CLHS PX8 SUPPORTED PARAMETERS                                                     | 58        |

| Camera Related Capabilities                                                              | 58        |

| Camera Related Parameters                                                                | 58        |

| VIC Related Parameters                                                                   | 59        |

| ACQ Related Parameters                                                                   | 63        |

| Transfer Related Capabilities                                                            | 64        |

| Transfer Related Parameters                                                              | 64        |

| General Outputs #1: Related Capabilities (for GIO Module #0)                             | 65        |

| General Outputs #1: Related Parameters (for GIO Module #0)                               | 65        |

| General Inputs #1: Related Capabilities (for GIO Module #1)                              | 65        |

| General Inputs #1: Related Parameters (for GIO Module #1)                                | 65        |

| Bidirectional General I/Os: Related Capabilities (for GIO Module #2)                     | 65        |

| Bidirectional General I/Os: Related Parameters (for GIO Module #2)                       | 66        |

| SAPERA SERVERS AND RESOURCES                                                             | 67        |

| WINDOWS EMBEDDED 7 INSTALLATION                                                          | 68        |

| TECHNICAL SPECIFICATIONS                                                                 | 69        |

| XTIUM2-CLHS PX8 BOARD SPECIFICATIONS                                                     | 69        |

| HOST SYSTEM REQUIREMENTS                                                                 | 70        |

| EMI CERTIFICATIONS                                                                       | 71        |

|                                                                                          |           |

|    | CONNECTOR AND SWITCH LOCATIONS                                           | 72  |

|----|--------------------------------------------------------------------------|-----|

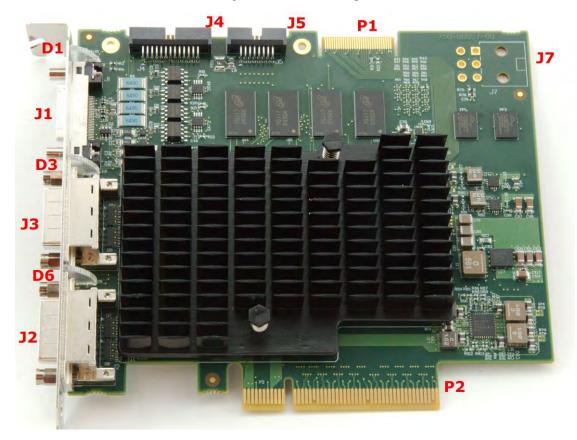

|    | Xtium2-CLHS PX8 Board Layout Drawing                                     | 72  |

|    | Connector / LED Description List                                         | 72  |

|    | CONNECTOR AND SWITCH SPECIFICATIONS                                      | 73  |

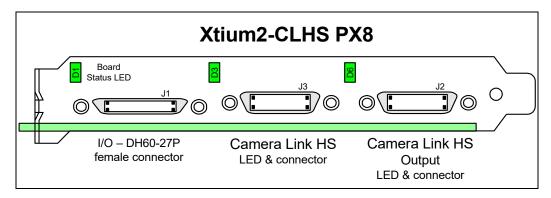

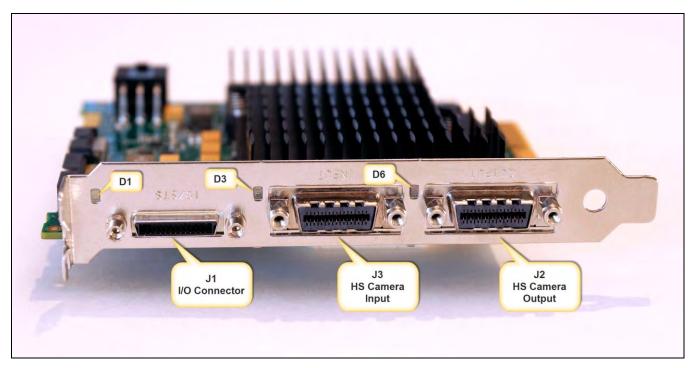

|    | Xtium2-CLHS PX8 End Bracket Detail                                       | 73  |

|    | Data Forwarding Setup                                                    | 74  |

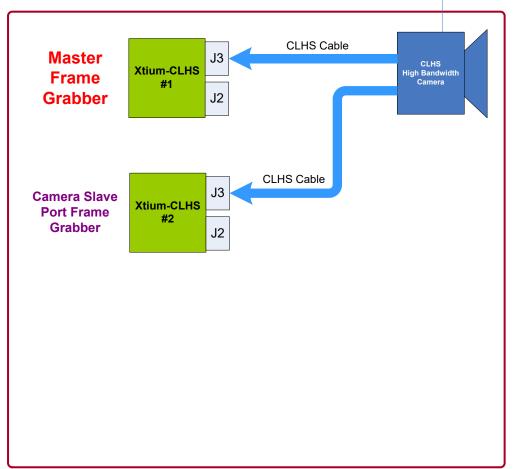

|    | Connecting to Dual Output CLHS Camera                                    | 76  |

|    | Status LEDs Functional Descriptions                                      | 77  |

|    | D1: Boot-up/PCIe Status LED                                              | 77  |

|    | D3: Camera Link HS Status LED (when a camera is connected)               | 77  |

|    | D3: Camera Link HS Status LED (as Data Forwarding receiver)              | 77  |

|    | D6: Data Forwarding Status LED                                           | 78  |

|    | J2: Data Forwarding Connector                                            | 78  |

|    | J3: Camera Link HS Connector                                             | 79  |

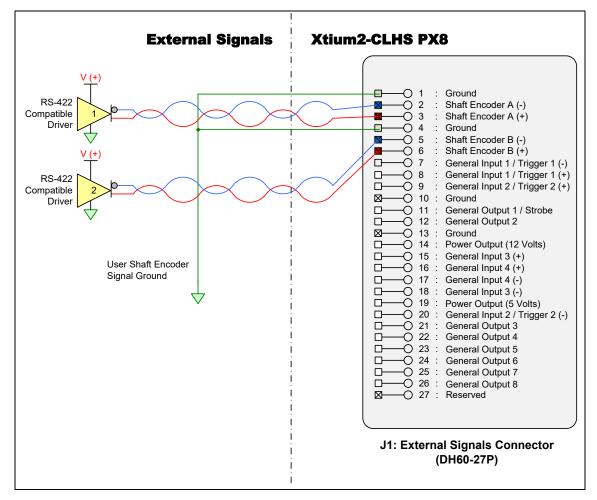

|    | J1: External I/O Signals Connector (Female DH60-27P)                     | 79  |

|    | J4: Internal I/O Signals Connector (26-pin SHF-113-01-L-D-RA)            | 79  |

|    | Note 1: General Inputs / External Trigger Inputs Specifications          | 80  |

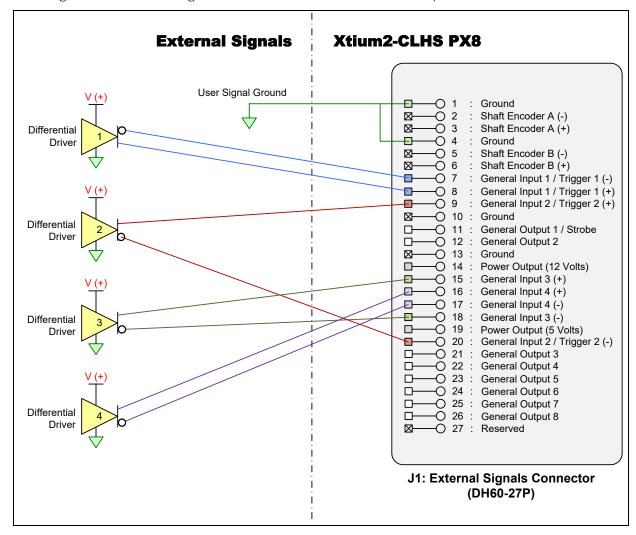

|    | Block Diagram: Connecting External Drivers to General Inputs on J1       | 82  |

|    | External Driver Electrical Requirements                                  | 82  |

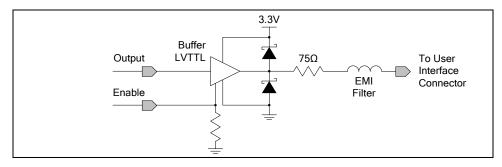

|    | Note 2: General Outputs /Strobe Output Specifications                    | 83  |

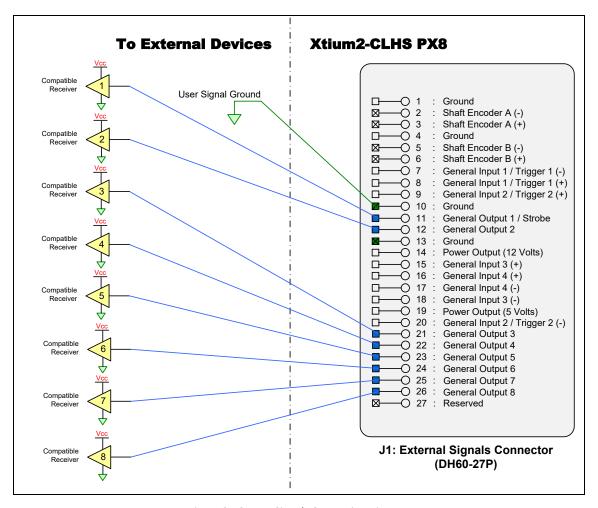

|    | Block Diagram: Connecting External Receivers to the General Outputs      | 84  |

|    | External Receiver Electrical Requirements                                | 84  |

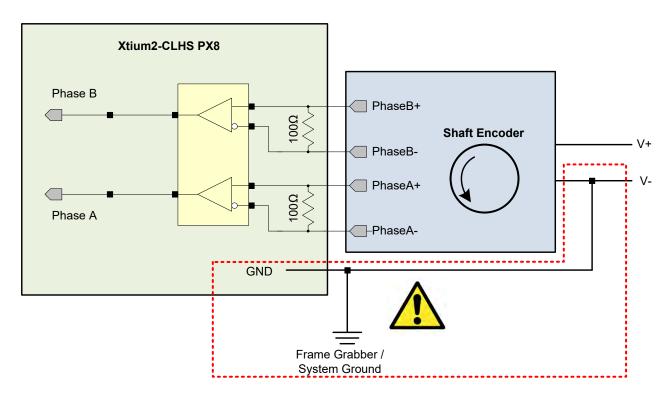

|    | Note 3: RS-422 Shaft Encoder Input Specifications                        | 85  |

|    | Example: Connecting to the RS-422 Shaft Encoder Block Diagram            | 86  |

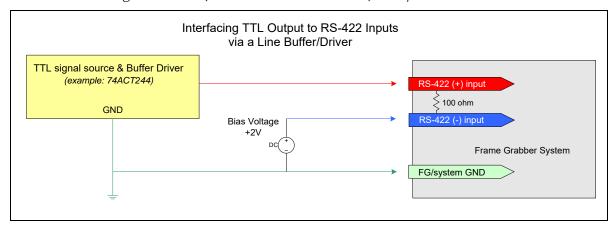

|    | Note 3.2: Interfacing to a TTL (also called Push-Pull) Output            | 87  |

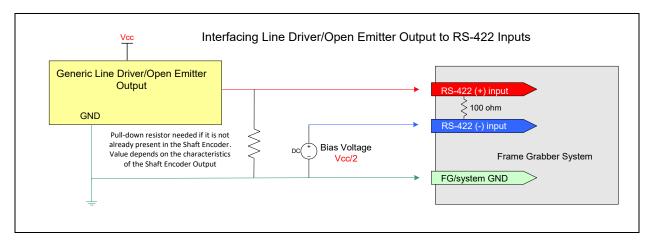

|    | Note 3.3: Interfacing to a Line Driver (also called Open Emitter) Output | 87  |

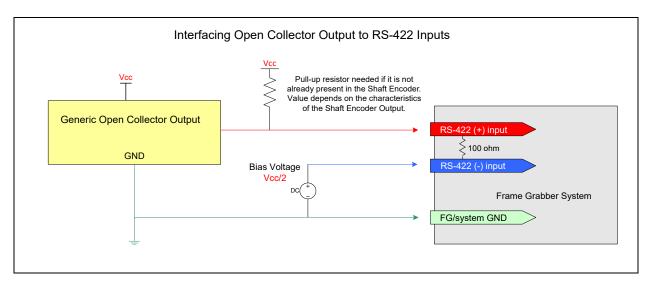

|    | Note 3.4: Interfacing to an Open Collector Output                        | 88  |

|    | J5: Multi-Board Sync / Bi-directional General I/Os                       | 89  |

|    | Hardware Preparation                                                     | 89  |

|    | Configuration via Sapera Application Programming                         | 89  |

|    | Configuration via Sapera CamExpert                                       | 89  |

|    | Cables & Accessories                                                     | 91  |

|    | Camera Link HS Cables Overview and Resources                             | 91  |

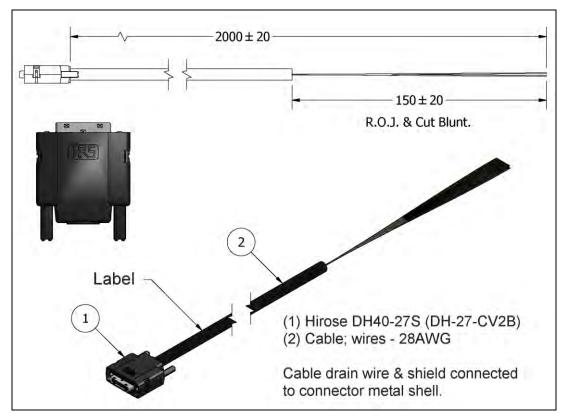

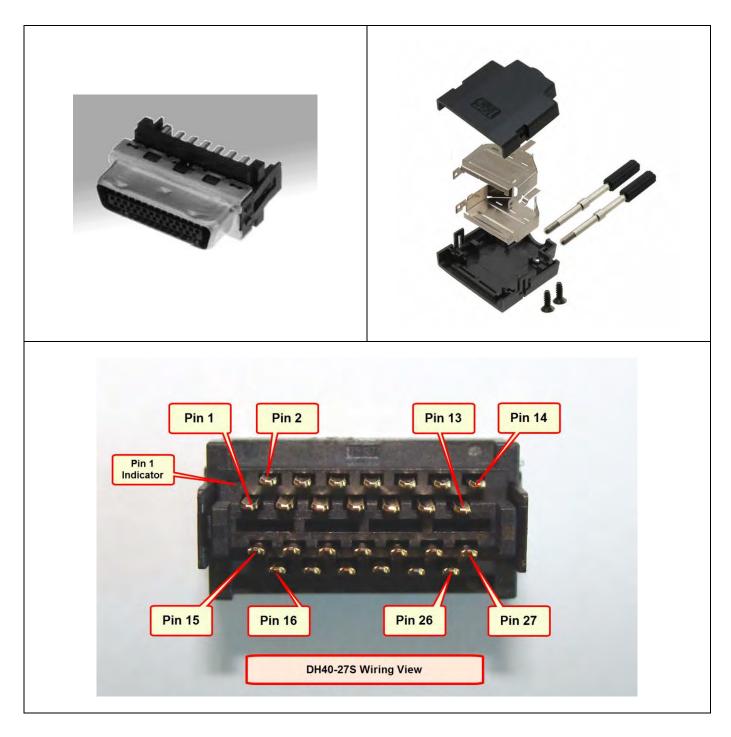

|    | DH40-27S Cable to Blunt End (OR-YXCC-27BE2M1, Rev B1)                    | 92  |

|    | DH40-27S Connector Kit for Custom Wiring                                 | 93  |

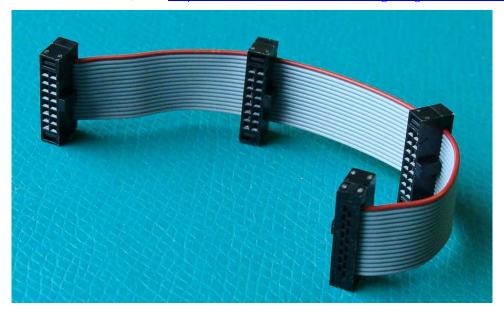

|    | Cable assemblies for I/O connector J4                                    | 94  |

|    | Teledyne DALSA I/O Cable (part #OR-YXCC-TIOF120)                         | 94  |

|    | Third Party I/O Cables for J4                                            | 94  |

|    | Board Sync Cable Assembly OR-YXCC-BSYNC40                                | 95  |

| СА | MERA LINK HS INTERFACE                                                   | 96  |

|    | CAMERA LINK HS OVERVIEW                                                  | 96  |

|    | Rights and Trademarks                                                    | 96  |

| ΑP | PENDIX A: SILENT INSTALLATION                                            | 97  |

|    | SILENT MODE INSTALLATION                                                 | 97  |

|    | Creating a Response File                                                 | 97  |

|    | Running a Silent Mode Installation                                       | 98  |

|    | SILENT MODE UNINSTALL                                                    | 98  |

|    | Creating a Response File                                                 | 98  |

|    | Running a Silent Mode Uninstall                                          | 98  |

|    | SILENT MODE INSTALLATION RETURN CODE                                     | 99  |

|    | Installation Setup with CorAppLauncher.exe                               | 99  |

|    |                                                                          | 100 |

|    | 9                                                                        | 100 |

|    | Run the Installation using install ini                                   | 100 |

| APPENDIX B: TROUBLESHOOTING PROBLEMS                       | 101 |

|------------------------------------------------------------|-----|

| Overview                                                   | 101 |

| PROBLEM TYPE SUMMARY                                       | 101 |

| First Step: Check the Status LED                           | 101 |

| Possible Installation Problems                             | 101 |

| Possible Functional Problems                               | 102 |

| Troubleshooting Procedures                                 | 102 |

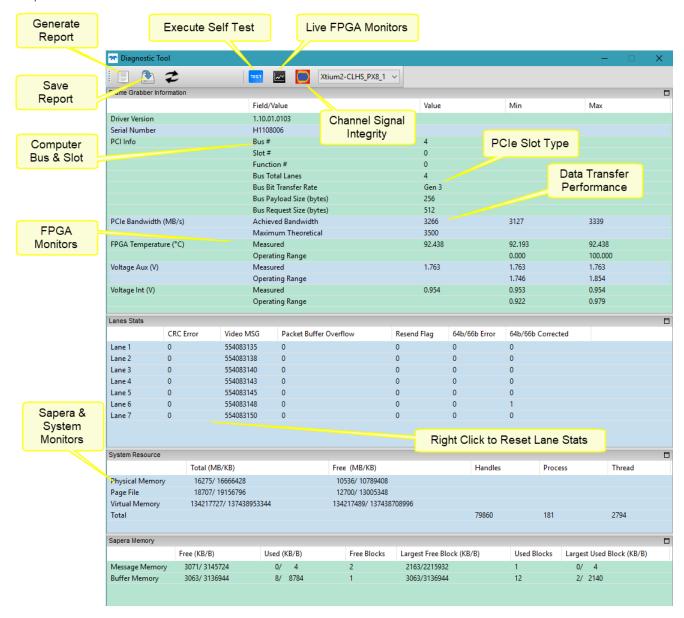

| Diagnostic Tool Overview                                   | 102 |

| Diagnostic Tool Main Window                                | 103 |

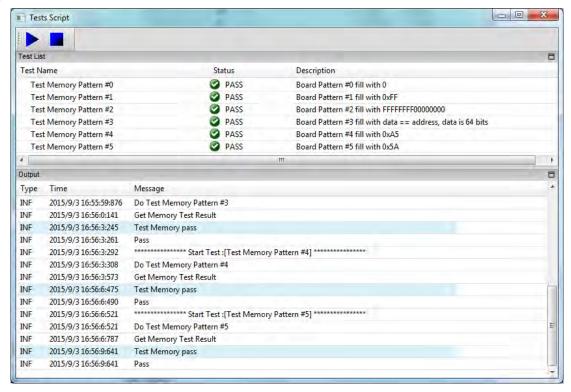

| Diagnostic Tool Self-Test Window                           | 104 |

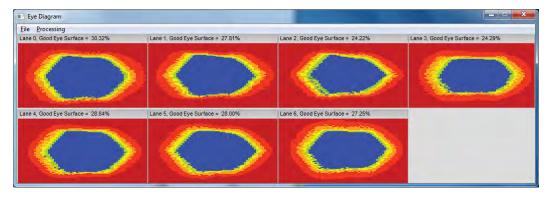

| Camera Input Eye Diagram Monitor                           | 104 |

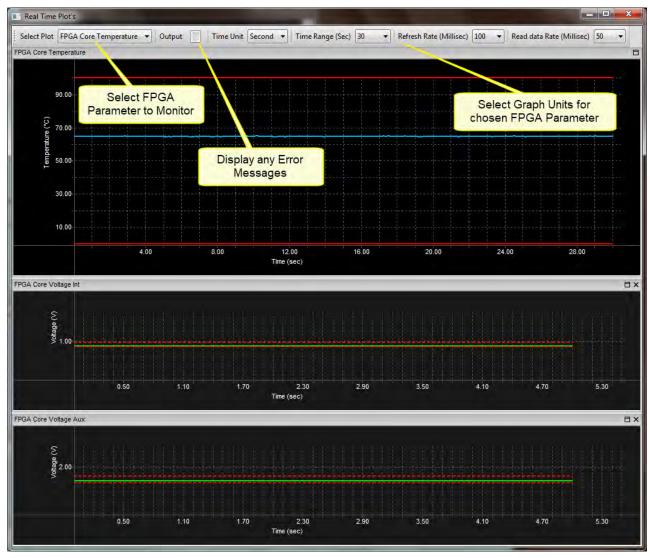

| Diagnostic Tool Live Monitoring Window                     | 105 |

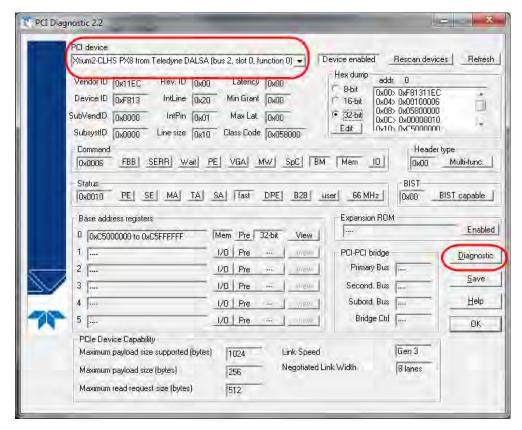

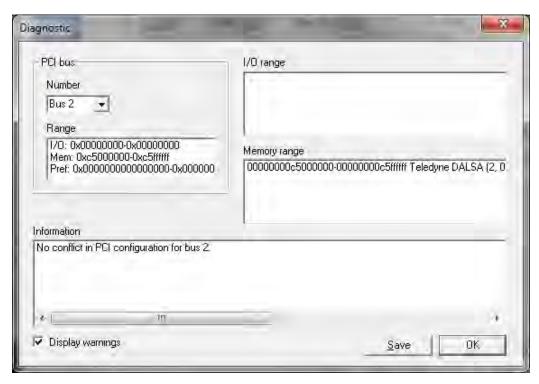

| Checking for PCI Bus Conflicts                             | 105 |

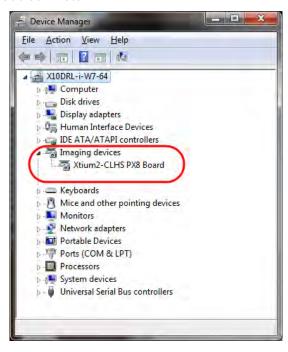

| Windows Device Manager                                     | 107 |

| BSOD (blue screen) Following a Board Reset                 | 108 |

| Sapera and Hardware Windows Drivers                        | 108 |

| Recovering from a Firmware Update Error                    | 108 |

| Driver Information via the Device Manager Program          | 109 |

| Teledyne DALSA Log Viewer                                  | 110 |

| On-board Image Memory Requirements for Acquisitions        | 110 |

| Symptoms: CamExpert Detects no Boards                      | 110 |

| Troubleshooting Procedure                                  | 110 |

| Symptoms: Xtium2-CLHS PX8 Does Not Grab                    | 111 |

| Symptoms: Card grabs black                                 | 111 |

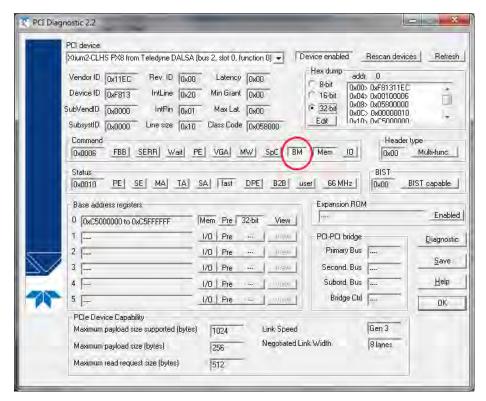

| Symptoms: Card acquisition bandwidth is less than expected | 112 |

| CONTACT INFORMATION                                        | 113 |

| SALES INFORMATION                                          | 113 |

| TECHNICAL SUPPORT                                          | 113 |

# Figures

| Figure 1: Automatic Firmware Update                                                      | 16  |

|------------------------------------------------------------------------------------------|-----|

| Figure 2: Manual Firmware Update                                                         | 17  |

| Figure 3: Start Menu Firmware Update Shortcut                                            | 18  |

| Figure 4: Board Information via Device Manager                                           | 20  |

| Figure 5: Device Manager File Menu Save Device Info Command                              | 23  |

| Figure 6: CamExpert Program                                                              | 26  |

| Figure 7: Xtium2-CLHS PX8 Block Diagram                                                  | 41  |

| Figure 8: Xtium2-CLHS Flow Diagram                                                       | 42  |

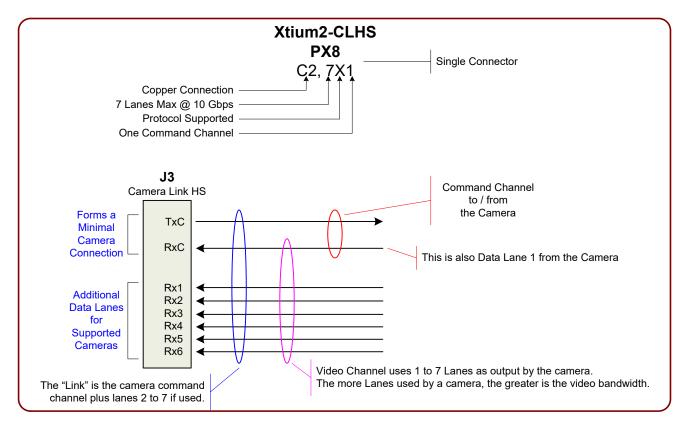

| Figure 9: CLHS Camera Interface                                                          | 43  |

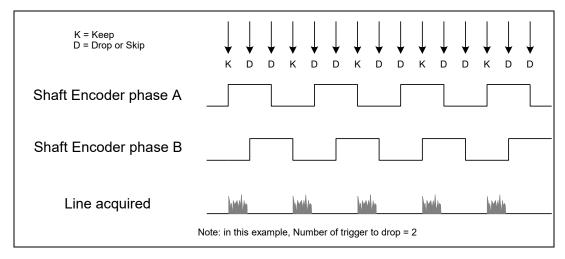

| Figure 10: Encoder Input with Pulse-drop Counter                                         | 45  |

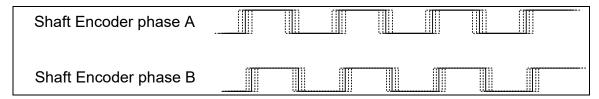

| Figure 11: Using Shaft Encoder Direction Parameter                                       | 45  |

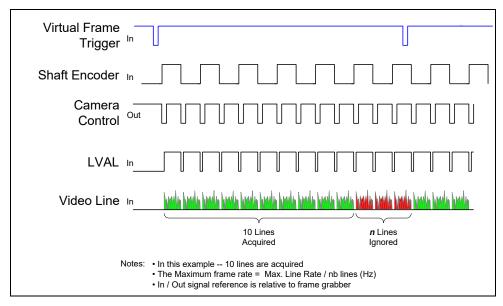

| Figure 12: Synchronization Signals for a 10 Line Virtual Frame                           | 47  |

| Figure 13: Line scan, Fixed Frame, No Trigger                                            | 48  |

| Figure 14: Line scan, Fixed Frame, Edge Trigger                                          | 48  |

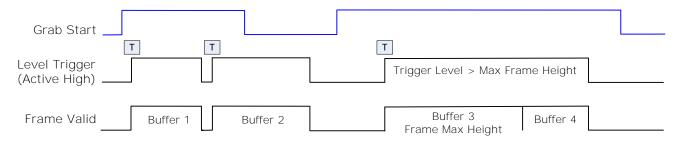

| Figure 15: Line scan, Fixed Frame, Level Trigger (Roll-Over to Next Frame)               | 48  |

| Figure 16: Line scan, Variable Frame, Edge Trigger (Active High determines Frame Length) | 49  |

| Figure 17: Line scan, Fixed Frame, Level Trigger (Roll-Over)                             | 49  |

| Figure 18: EMI Certifications                                                            | 71  |

| Figure 19: Board Layout                                                                  | 72  |

| Figure 20: End Bracket Details                                                           | 73  |

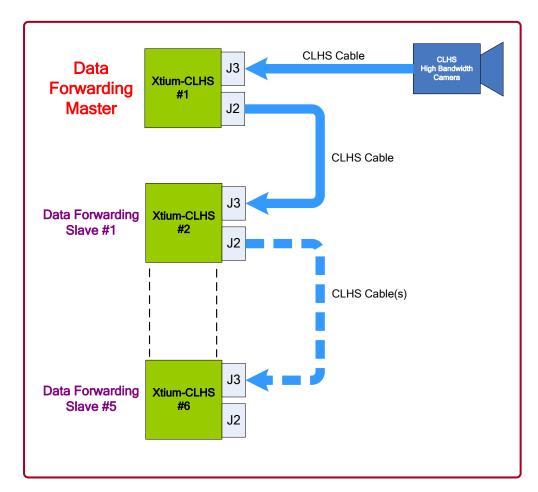

| Figure 21: Data Forwarding Block Diagram                                                 | 75  |

| Figure 22: Dual Camera Output Connection Block Diagram                                   | 76  |

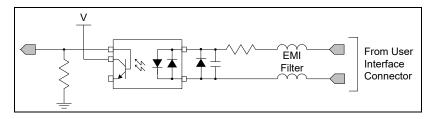

| Figure 23: General Inputs Electrical Diagram                                             | 80  |

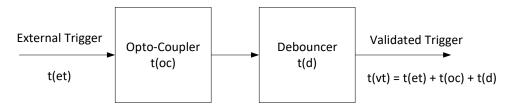

| Figure 24: External Trigger Input Validation & Delay                                     | 81  |

| Figure 25: External Signals Connection Diagram                                           | 82  |

| Figure 26: General Outputs Electrical Diagram                                            | 83  |

| Figure 27: Output Signals Connection Diagram                                             | 84  |

| Figure 28: RS-422 Shaft Encoder Input Electrical Diagram                                 | 85  |

| Figure 29: External RS-422 Signals Connection Diagram                                    | 86  |

| Figure 30: Interfacing TTL to RS-422 Shaft Encoder Inputs                                | 87  |

| Figure 30: Interfacing to a Line Driver Output                                           | 87  |

| Figure 30: Interfacing to an Open Collector Output                                       | 88  |

| Figure 31: DH60-27P Cable No. OR-YXCC-27BE2M1 Detail                                     | 92  |

| Figure 32: Photo of cable OR-YXCC-27BE2M1                                                | 92  |

| Figure 33: I/O Cable #OR-YXCC-TIOF120                                                    | 94  |

| Figure 34: Photo of cable OR-YXCC-BSYNC40                                                | 95  |

| Figure 35: Create an install in File                                                     | 100 |

| Figure 39: Diagnostic Tool "Resource in use"                                             | 102 |

| Figure 39: Diagnostic Tool User Interface                                                | 103 |

| Figure 39: Diagnostic Tool Self-Test Window                                              | 104 |

| Figure 39: Diagnostic Tool Eye Diagram                                                   | 104 |

| Figure 36: PCI Diagnostic Program                                                        | 106 |

| Figure 37: PCI Diagnostic Program - PCI bus info                                         | 107 |

| Figure 38: Using Windows Device Manager                                                  | 107 |

| Figure 39: Board Firmware Version                                                        | 109 |

| Figure 39: PCI Diagnostic Tool BM Button                                                 | 111 |

# Overview

# **Product Part Numbers**

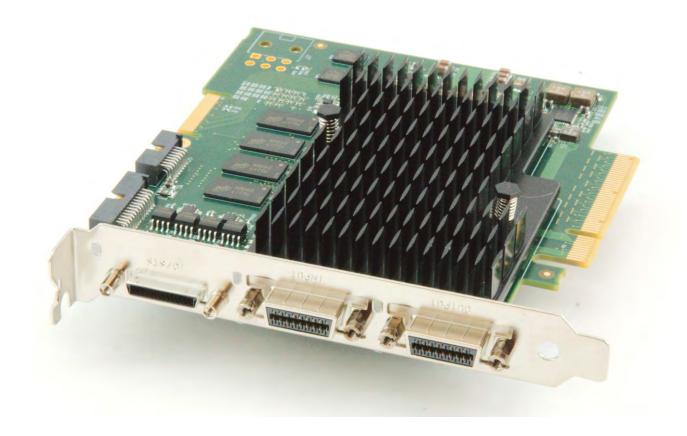

#### Xtium2-CLHS PX8 Board

| Item                                                                  | Product Number |

|-----------------------------------------------------------------------|----------------|

| Xtium2-CLHS PX8                                                       | OR-A8S0-PX870  |

| For OEM clients, this manual in printed form, is available on request | OC-A8SM-PX8U0  |

#### Xtium2-CLHS PX8 Software

| Item                                                                                                                                                                                                                                               | Product Number                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Sapera LT version 8.30 or later for full feature support (required but sold separately)                                                                                                                                                            | OC-SL00-0000000                    |

| <ol> <li>Sapera LT:         Provides everything needed to build imaging application     </li> <li>Current Sapera compliant board hardware drivers</li> <li>Sapera documentation:         (compiled HTML help, Adobe Acrobat® (PDF)     </li> </ol> |                                    |

| (optional) Sapera Processing Imaging Development Library includes over 600 optimized image-processing routines.                                                                                                                                    | Contact Sales at<br>Teledyne DALSA |

### Optional Xtium2-CLHS PX8 Cables & Accessories

| Item                                                                                                                            | Product Number                     |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| DH40-27S cable assembly to blunt end: 6 ft. cable I/O 27 pin Hirose connector to blunt end. This cable assembly connects to J1. | OR-YXCC-27BE2M1                    |

| Cable set to connect to J4 Internal I/O Signals connector (J4: 26-pin SHF-113-01-L-D-RA)                                        | see suggested cables               |

| DH40-27S Connector Kit for Custom Wiring:<br>Comprised of a DH40-27S connector plus screw lock housing kit                      | OR-YXCC-H270000                    |

| Cable assembly to connect to J5 (Board Sync)                                                                                    |                                    |

| Connecting 2 boards Connection 3 or 4 boards                                                                                    | OR-YXCC-BSYNC20<br>OR-YXCC-BSYNC40 |

| CX4 Cable:                                                                                                                      | Contact Sales at<br>Teledyne DALSA |

# About the Xtium2-CLHS PX8 Frame Grabber

### Series Key Features

- Compliant with Camera Link HS (CLHS) specification version 1.0 (X-Protocol) (visit http://www.visiononline.org/vision-standards.cfm for details on industry standards)

- Supports up to 7 lanes.

- Bit transfer rate of 10 Gbps (requires cable length of less than 3m)

- The specification defines a device discovery methodology that can be automated and which provides plug and play capability

- Camera Link HS cameras implement GenICam and associated GenCP, thus resulting in ease of use for Teledyne DALSA or third party cameras

- Uses a PCIe x8 Gen3 slot to maximize transfers to host computer buffers

- Acquire from Monochrome and RGB CLHS cameras, both area scan and linescan

- Output lookup tables

- Vertical and Horizontal Flip supported on board

- External Input Triggers and Shaft Encoder inputs, along with Strobe outputs

- Supports Data Forwarding Mode, where camera image data is automatically transferred to one or more Xtium2-CLHS boards (each installed in a separate computer), allowing distributed processing of the acquisition.

- Supports Multi-board Sync for trigger events, to simultaneously acquire from multiple cameras.

- Supports a number of acquisition events in compliance with "Teledyne DALSA's Trigger to Image Reliability"

- RoHS compliant

See Technical Specifications for detailed information.

# User Programmable Configurations

Use the Xtium2-CLHS PX8 firmware loader function in the Teledyne DALSA Device manager utility to select firmware for one of the supported modes. Firmware selection is made either during driver installation or manually later on (see Firmware Update: Manual Mode). Currently there is only one firmware version available:

Camera Link HS camera (installation default):

Support for 1 Camera Link HS camera: either monochrome 8/10/12/14/16 bits per pixel or RGB 8 bits per pixel.

# ACUPIus: Acquisition Control Unit

ACUPIus consists of a grab controller, one pixel packer, and one time base generator.

ACUPlus acquires variable frame sizes up to 64KB per horizontal line and up to 16 million lines per frame. ACUPlus can also capture an infinite number of lines from a line scan camera without losing a single line of data.

## DTE: Intelligent Data Transfer Engine

The Xtium2-CLHS PX8 intelligent Data Transfer Engine ensures fast image data transfers between the board and the host computer with zero CPU usage. The DTE provides a high degree of data integrity during continuous image acquisition in a non-real time operating system like Windows. DTE consists of intelligent DMA units with auto-loading Scatter-Gather tables.

### PCI Express x8 Gen3 Interface

The Xtium2-CLHS PX8 is a universal PCI Express x8 Gen3 board, compliant with the PCI Express 3.0 specification. The Xtium2-CLHS PX8 board achieves transfer rates up to 7.0Gbytes/sec. to host memory. Note that performance can be lower depending on PC and/or programmed configuration.

The Xtium2-CLHS PX8 board occupies one PCI Express x8 Gen3 expansion slot and one chassis opening.

#### Important:

- To obtain the maximum transfer rate to host memory, make sure the Xtium2-CLHS PX8 is in a computer with a Gen3 slot. The board will work in a Gen1, Gen2 or Gen3 slot, but only with a quarter or half the possible transfer performance respectively.

- The system motherboard BIOS should allow setting the PCIe maximum payload size to 256 or higher. Systems with fixed settings of 128 will limit performance for transfers to host memory.

- If the computer only has a PCI Express x16 slot, test directly (use the supplied <u>diagnostic tool</u>) or review the computer documentation to know if the Xtium2-CLHS PX8 is supported. Computer motherboards may only support x16 graphic video board products in x16 slots.

#### Advanced Controls Overview

#### Visual Indicators

Xtium2-CLHS PX8 features 3 LED indicators to facilitate system installation and setup (see <u>Status LEDs Functional Descriptions</u>). These indicators provide visual feedback on the board status and camera status.

#### External Event Synchronization

Trigger inputs and strobe signals precisely synchronize image captures with external events.

#### Camera Link HS Communication Port

A single Sapera LT Acquisition Device provides access to the Camera Link HS camera configuration via the board device driver. The communication port presents a seamless interface to access GenICam camera features.

#### Quadrature Shaft Encoder

An important feature for web scanning applications, the Quadrature Shaft Encoder inputs allow synchronized line captures from external web encoders (see <u>J1- I/O Connector</u>). The Xtium2-CLHS PX8 provides a RS-422 input that supports a tick rate of up to 5 MHz.

# Development Software Overview

## Sapera++ LT Library

Sapera++ LT is a powerful development library for image acquisition and control. Sapera++ LT provides a single API across all current and future Teledyne DALSA hardware. Sapera++ LT delivers a comprehensive feature set including program portability, versatile camera controls, flexible display functionality and management, plus easy to use application development wizards. Applications are developed using either C++ or .NET frameworks.

Sapera++ LT comes bundled with CamExpert, an easy to use camera configuration utility to create new, or modify existing camera configuration files.

## Sapera Processing Library

Sapera Processing is a comprehensive set of C++ classes or .NET classes for image processing and analysis. Sapera Processing offers highly optimized tools for image processing, blob analysis, search (pattern recognition), OCR and barcode decoding.

# Quick Start Setup & Installation

The following procedure outlines the basic steps required to install the Teledyne DALSA Xtium2-CLHS PX8. For complete installation details and information, see Installing Xtium2-CLHS PX8.

Install the Xtium2-CLHS PX8 in an available PCle x8 slot on the host computer.

2

Download and install the Sapera LT SDK software from the Teledyne DALSA website.

http://teledynedalsa.com/imaging/support/downloads/sdks/

#### Software Development Kits

Access to certain drivers and SDK updates are restricted to Teledyne DALSA customers that have registered their development package (SDK). If you have not yet done so, please register your software before proceeding.

| Description                                  | Version | Release Date |

|----------------------------------------------|---------|--------------|

| Sapera LT SDK (full version) - Free Download | 8.20    | 10/28/2016   |

3

Download and install the Xtium2-CLHS PX8 device driver from the Teledyne DALSA website.

https://www.teledynedalsa.com/imaging/support/downloads/drivers/

To complete the installation, <u>update the Xtium2-CLHS PX8 firmware</u> when prompted; select Automatic to update the firmware (only one firmware option is available, support for one Camera Link HS camera).

Reboot when all software and board drivers are installed.

5

Launch <u>Sapera LT CamExpert</u> to verify the installation; the board should be present in the list of available devices.

Connect camera to the board Camera Link HS input connector. Ensure camera is properly powered.

7

When CamExpert detects a camera (as per the CLHS device discovery protocol), camera parameters are displayed along with the board parameters.

When properly connected, the video status bar displays camera signals in green.

Video status: 10.000 Gb/s | Lane 1 Lock | Lane 2 Lock | Lane 3 Lock | Lane 4 Lock | Lane 5 Lock | Lane 6 Lock | Lane 7 Lock | Frame Valid | Line Valid | PoCL | PoCL 2

8

Click Grab to acquire a test image to validate the setup.

Modify the board and camera parameters as necessary. When completed, save the <u>camera configuration file</u>.

The Xtium2-CLHS PX8 can be configured using the parameter settings in this file when using the Sapera LT API in your application to acquire images

# Installing Xtium2-CLHS PX8

# Warning! (Grounding Instructions)

Static electricity can damage electronic components. Please discharge any static electrical charge by touching a grounded surface, such as the metal computer chassis, before performing any hardware installation. If you do not feel comfortable performing the installation, please consult a qualified computer technician.

Important: Never remove or install any hardware component with the computer power on. Disconnect the power cord from the computer to disable the power standby mode. This prevents the case where some computers unexpectedly power up when a board is installed.

# Installation

The installation sequence is as follows:

- Install the board hardware into an available PCI Express x8 Gen3 slot.

- Turn on the computer.

- Install the Sapera LT Development Library or only its 'runtime library'.

- Install the Xtium2-CLHS PX8 Sapera board driver.

- Update the board firmware if required.

- Reboot the computer.

- Connect a CLHS camera and test.

For information on performing a silent installation, refer to Appendix A: Silent Installation. For troubleshooting installation problems, refer to Appendix B: Troubleshooting Problems.

#### Hardware Installation

- Turn the computer off, disconnect the power cord (disables power standby mode), and open the computer chassis to allow access to the expansion slot area.

- Install the Xtium2-CLHS PX8 into a free PCI Express x8 Gen3 expansion slot. Note that some computer's x16 slot may support boards such as the Xtium2-CLHS PX8, not just display adapters.

- Close the computer chassis and turn the computer on.

- Logon to the computer as administrator or with an account that has administrator privileges.

- <u>Connect a CLHS camera</u> to J3 after installing Sapera as described below. Test with <u>CamExpert</u>.

#### Multi-board Data Forwarding Hardware Setup

• For distributed processing applications, see Data Forwarding Setup for information about data forwarding cabling with one to six Xtium2-CLHS boards.

#### Multi-board Sync & I/O Setup

• For multi-board sync applications, see J5: Multi-Board Sync / Bi-directional General I/Os for information on using two to four Xtium2-CLHS boards in one computer.

## Sapera LT Library & Xtium2-CLHS PX8 Driver Installation

Sapera LT SDK (full version), the image acquisition and control SDK for Teledyne DALSA cameras and frame grabbers is available for download from the Teledyne DALSA website:

http://teledynedalsa.com/imaging/support/downloads/sdks/

Run-time versions are also available for download at this location.

# Software Development Kits

Access to certain drivers and SDK updates are restricted to Teledyne DALSA customers that have registered their development package (SDK). If you have not yet done so, please register your software before proceeding.

| Description                                  | Version | Release Date |

|----------------------------------------------|---------|--------------|

| Sapera LT SDK (full version) - Free Download | 8.30    | 05/19/2017   |

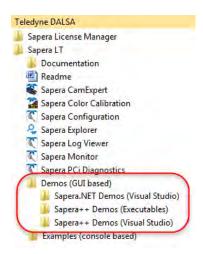

The Sapera LT SDK installation includes compiled demo and example programs, along with project source code, in both C++ and .NET languages, for most Microsoft Visual Studio development platforms. The Sapera LT ++ and Sapera LT .NET demo source code are found in the Sapera\Demos directory.

Refer to Sapera LT User's Manual for additional details about Sapera LT.

Teledyne DALSA Device Drivers

All Teledyne DALSA device drivers are available for download from the Teledyne DALSA website:

https://www.teledynedalsa.com/imaging/support/downloads/drivers/

#### Installation Procedure

- Sapera LT is installed <u>before</u> Teledyne DALSA board drivers.

- Download the Sapera LT SDK from the Teledyne DALSA website and run the executable file; the installation menu is presented.

- The installation program may prompt to reboot the computer. It is not necessary to reboot the computer between the installation of Sapera LT and the board driver.

- Download the Xtium2-CLHS PX8 device driver from the Teledyne DALSA website and run the executable file; the installation menu is presented.

- During the late stages of the installation, the <u>Xtium2-CLHS PX8 firmware loader</u> application starts.

- Reboot when all software and board drivers are installed.

If Windows displays any unexpected message concerning the board, power off the system and verify the Xtium2-CLHS PX8 is installed in the slot properly. You should also note the board's status LED color and compare it to the defined LED states as described in <a href="D1: Boot-up/PCIe">D1: Boot-up/PCIe</a> Status LED.

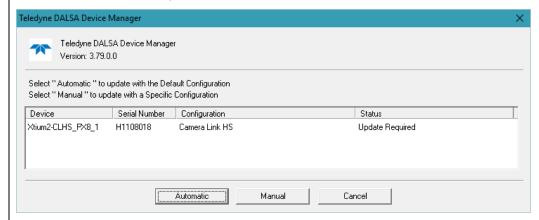

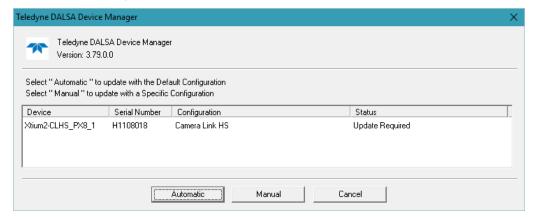

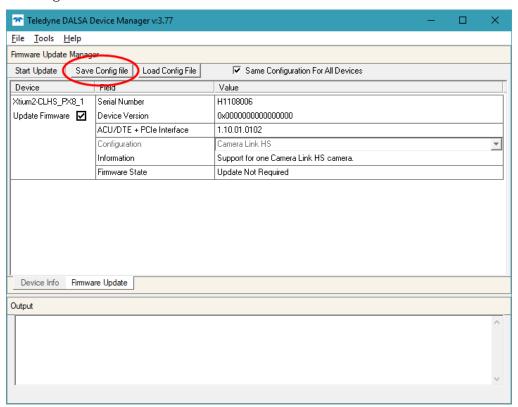

#### Xtium2-CLHS PX8 Firmware Loader

The Device Manager-Firmware Loader program automatically executes at the end of the driver installation and on every subsequent reboot of the computer. It will determine if the Xtium2-CLHS PX8 requires a firmware update. If firmware is required, a dialog displays. This dialog also allows the user to load alternative firmware if available for the Xtium2-CLHS PX8.

*Important*: In the rare case of firmware loader errors please see Recovering from a Firmware Update Error.

#### Firmware Update: Automatic Mode

Click Automatic to update the Xtium2-CLHS PX8 firmware. The Xtium2-CLHS PX8 currently supports one firmware configuration.

See User Programmable Configurations for details on all supported modes, selected via a manual update of alternative firmware.

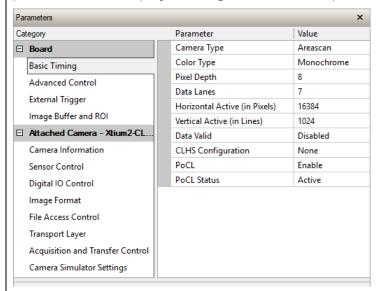

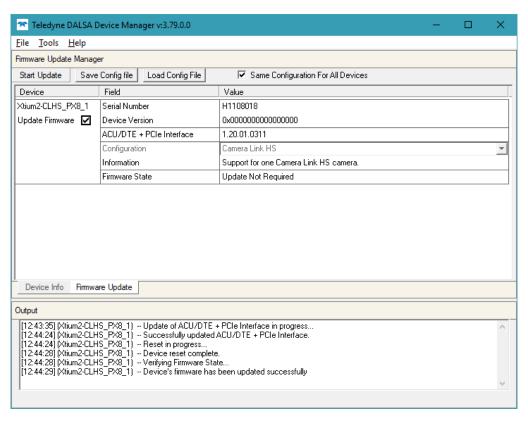

With multiple Xtium2-CLHS PX8 boards in the system, all boards update with new firmware. If any installed Xtium2-CLHS PX8 board installed in a system already has the correct firmware version, an update is not required. In the following screen shot, a single Xtium2-CLHS PX8 board is installed and ready for a firmware upgrade.

Figure 1: Automatic Firmware Update

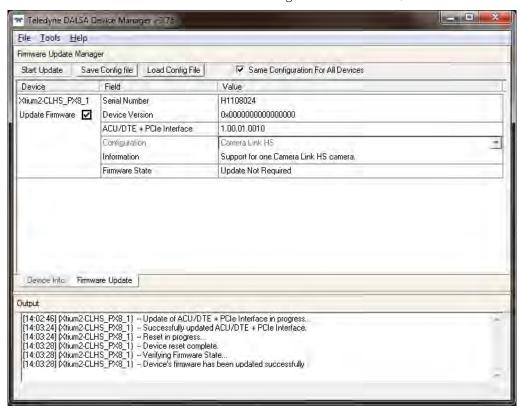

#### Firmware Update: Manual Mode

Select Manual mode to load firmware other then the default version or when, in the case of multiple Xtium2-CLHS PX8 boards in the same system, if each requires different firmware.

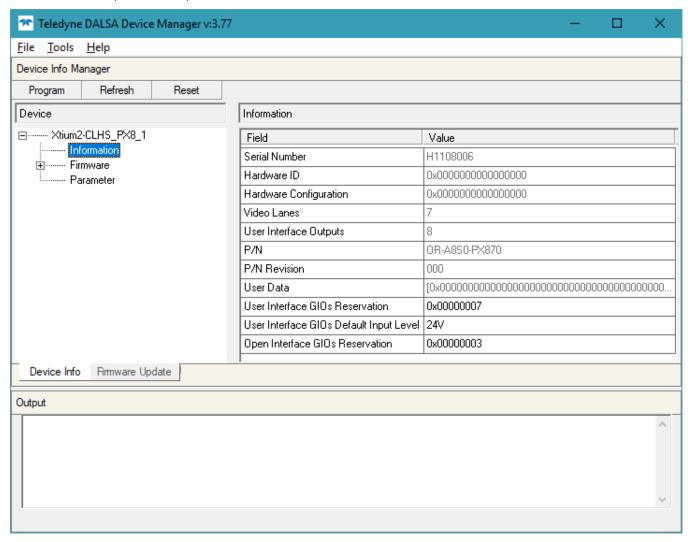

The following figure shows the Device Manager manual firmware screen. Displayed is information on all installed Xtium2-CLHS PX8 boards, their serial numbers, and their firmware components.

#### Performing a Manual Firmware Update

- Select the Xtium2-CLHS PX8 to update via the board selection box (if there are multiple boards in the system).

- From the Configuration field drop menu select the firmware version required (typical required or offered to support different CLHS cameras).

- Click on the Start Update button.

- Observe the firmware update progress in the message output window.

- Close the Device manager program when the device reset complete message shows.

Figure 2: Manual Firmware Update

#### Executing the Firmware Loader from the Start Menu

If required, the Xtium2-CLHS PX8 Firmware Loader program is executed via the Windows Start Menu shortcut **Start ● Programs ●** Teledyne **DALSA ●** Xtium2-CLHS PX8 **Driver ● Firmware** Update.

Figure 3: Start Menu Firmware Update Shortcut

A firmware change after installation is required to select a different configuration mode, if available; see User Programmable Configurations.

# Upgrading Sapera or Board Driver

When installing a new version of Sapera or a Teledyne DALSA acquisition board driver in a computer with a previous installation, the current version must be un-installed first. Described below are two upgrade situations. Note that if the board is installed in a different slot, the new hardware wizard opens. Answer as instructed in the section Installation.

## Board Driver Upgrade Only

Minor upgrades to acquisition board drivers are distributed as ZIP files available in the Teledyne DALSA web site <a href="www.teledynedalsa.com/mv/support">www.teledynedalsa.com/mv/support</a>. Board driver revisions are also available on the next release of the Sapera Essential CD-ROM.

Often minor board driver upgrades do not require a new revision of Sapera. To confirm that the current Sapera version will work with the new board driver:

- Check the new board driver ReadMe file before installing, for information on the minimum Sapera version required.

- If the ReadMe file does not specify the Sapera version required, contact Teledyne DALSA Technical Support (see Technical Support).

#### To upgrade the board driver only:

- Logon the computer as an administrator or with an account that has administrator privileges.

- In Windows 7, from the start menu select **Start Settings Control Panel Programs** and Features. Double-Click the Teledyne DALSA Xcelera board driver and click Remove.

- In Windows 8 & Windows 10, just type Control Panel while in the start screen, or click the arrow in the lower left side to bring up the all applications window. Select Programs and Features, then double-click the Teledyne DALSA Xcelera board driver and click Remove.

- Install the new board driver. Run Setup.exe if installing manually from a downloaded driver file.

- Important: You cannot install a Teledyne DALSA board driver without Sapera LT installed on the computer.

## Upgrading both Sapera and Board Driver

When upgrading both Sapera and the acquisition board driver, follow the procedure described below.

- Logon the computer as an administrator or with an account that has administrator privileges.

- In Windows 7, from the start menu select **Start Settings Control Panel Programs** and Features. Double-click the Teledyne DALSA Xcelera board driver and click Remove. Follow by also removing the older version of Sapera LT.

- In Windows 8 & Windows 10, just type Control Panel while in the start screen, or click the arrow in the lower left side to bring up the all applications window. Select Programs and Features, then double-click the Teledyne DALSA Xcelera board driver and click Remove. Follow by also removing the older version of Sapera LT.

- Reboot the computer and logon the computer as an administrator again.

- Install the new versions of Sapera and the board driver as if this was a first time installation. See Sapera LT Library & Xtium2-CLHS PX8 Driver Installation for installation procedures.

# Displaying Xtium2-CLHS PX8 Board Information

The Device Manager program also displays information about the Xtium2-CLHS PX8 boards installed in the system. To view board information run the program via the Windows Start Menu shortcut **Start ● Programs ●** Teledyne **DALSA ●** Xtium2-CLHS PX8 **Device Driver ● Device** Manager.

## Device Manager - Board Viewer

The following screen image shows the Device Manager program with the Information/Firmware tab active. The left window displays all Teledyne DALSA boards in the system and their individual device components. The right window displays the information stored in the selected board device. This example screen shows the Xtium2-CLHS PX8 board information.

Generate the Xtium2-CLHS PX8 device manager report file (BoardInfo.txt) by clicking File ● Save Device Info. Teledyne DALSA Technical Support may request this report to aid in troubleshooting installation or operational problems.

Figure 4: Board Information via Device Manager

Information Field Description

| Information Field                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Serial Number                              | [Read-Only]: Serial Number of the board.                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Hardware ID                                | [Read-Only]: Identifies hardware changes that affect the operation of the board. Currently there are no such changes.                                                                                                                                                                                                                                                                                                                   |  |

| Hardware Configuration                     | [Read-Only]: States the presence or absence of optional components. Currently there are no optional components available.                                                                                                                                                                                                                                                                                                               |  |

| Video Lanes                                | [Read-Only]: Indicates the maximum number of video lanes supported by the board. For this board, the value is 7.                                                                                                                                                                                                                                                                                                                        |  |

| User Interface Outputs                     | [Read-Only]: Number of available user interface outputs on the board. For this board, the value is 8.                                                                                                                                                                                                                                                                                                                                   |  |

| P/N                                        | [Read-Only]: Indicates the part number of the board.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| P/N Revision                               | [Read-Only]: Indicates the revision of the part number.                                                                                                                                                                                                                                                                                                                                                                                 |  |

| User Data                                  | [Read/Write]: This is a 64 byte general purpose user storage area. For information on how to read/write this field at the application level, contact Teledyne DALSA Technical Support.                                                                                                                                                                                                                                                  |  |

| User Interface GIOs<br>Reservation         | [Read/Write]: Use this field to reserve User Interface GIOs for use by the acquisition module. By default, boards are shipped with User Interface General Inputs 1 & 2 reserved for External Triggers and User Interface General Output 1 reserved for Strobe Output.  Click on the 'Value' field to open the dialog box show below. Disable any GIO reservations that are not required. Click the OK button to update the value field. |  |

|                                            | User Interface GIOs Reservation  Field  External Trigger Input #1  External Trigger Input #2  Strobe Output #1                                                                                                                                                                                                                                                                                                                          |  |

| User Interface GIOs<br>Default Input Level | [Read/Write]: Use this field to select the default input level of the User Interface GIOs.  Click on the 'Value' field to select the input signal level detection required.  User Interface GIOs Default Input Level TTL  Open Interface GIOs Reservation  11V 24V RS422  By default, boards are shipped with User Interface General Inputs set to 24V. Note that the input level can also be modified at the                           |  |

application level. Open Interface GIOs [Read/Write]: Use this field to reserve Open Interface GIOs for use by Reservation the acquisition module. To specify the open interface GIO reservations, click on the 'Value' field to open the Open Interface GIOs Reservation dialog box. Disable any GIO reservations that are not required. Click OK to update the value field. Open Interface GIOs Reservation ☑ Board Sync #1 ☑ Board Sync #2 1 • OK. Cancel By default, boards are shipped with Open Interface GIOs 1 & 2 reserved for Board Sync 1 & 2.

## Changing Device Settings

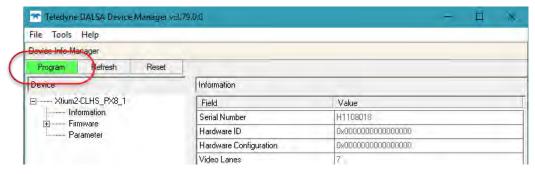

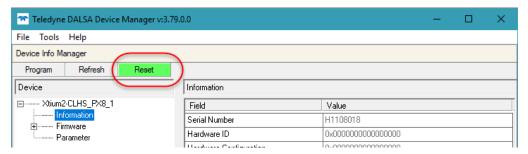

When device settings are changed, the board must be programmed and reset to effect the changes.

If board programming is required, the Program button is displayed in green; click the button to start programming.

When programming is complete, the Reset button is displayed in green, click the button to reset the board.

## Device Information Report

Teledyne DALSA Technical Support may request device information report to aid in troubleshooting installation or operational problems. Generate the Xtium2-CLHS PX8 device manager report file (BoardInfo.txt) by clicking **File • Save Device Info**.

Figure 5: Device Manager File Menu Save Device Info Command

# Configuring Sapera

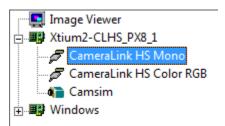

## Viewing Installed Sapera Servers

The Sapera configuration program (**Start ● Programs ●** Teledyne **DALSA ● Sapera LT ●** Sapera Configuration) allows the user to see all available Sapera servers for the installed Sapera-compatible boards. The System entry represents the system server. It corresponds to the host machine (your computer) and is the only server that should always be present.

### Increasing Contiguous Memory for Sapera Resources

The Contiguous Memory section lets the user specify the total amount of contiguous memory (a block of physical memory, occupying consecutive addresses) reserved for the resources needed for Sapera buffers allocation and Sapera messaging. For both items, the Requested value dialog box shows the 'CorMem' driver default memory setting while the Allocated value displays the amount of contiguous memory allocated successfully. The default values will generally satisfy the needs of most applications.

The Sapera buffers value determines the total amount of contiguous memory reserved at boot time for the allocation of dynamic resources used for frame buffer management such as scattergather list, DMA descriptor tables plus other kernel needs. Adjust this value higher if your application generates any out-of-memory error while allocating host frame buffers or when connecting the buffers via a transfer object.

You can approximate the worst-case scenario amount of contiguous memory required as follows:

Calculate the total amount of host memory used for one frame buffer

[number of pixels per line \* number of lines \* (2 if buffer is 10/12/14 or 16 bits)]

- Provide 200 bytes per frame buffer for Sapera buffer resources.

- Provide 64 bytes per frame buffer for metadata. Memory for this data is reserved in chunks of 64kB blocks.

- Provide 48 bytes per frame buffer for buffer management. Memory for this data is reserved in chunks of 64kB blocks.

- For each frame buffer DMA table, allocate 24 bytes + 8 bytes for each 4kB of buffer. For example, for a 120x50x8 image:

120 \* 50 = 6000 = 1.46 4kB blocks -> roundup to 2 4kB blocks

Therefore 24 bytes + (2 \* 8 bytes) = 40 bytes for DMA tables per frame buffer. Memory for this data is reserved in chunks of 64kB blocks. If vertical flipping is enabled, one must add 16 bytes per line per buffer. For example, for an image 4080x3072 image:

16 bytes \* 3072 = 49152 bytes

Note that Sapera LT reserves the 1<sup>st</sup> 5MB for its own resources, which includes the 200 bytes per frame buffer mentioned above.

• Test for any memory error when allocating host buffers. Simply use the Buffer menu of the Sapera Grab demo program (see Grab Demo Overview) to allocate the number of host buffers required for your acquisition source. Feel free to test the maximum limit of host buffers possible on your host system – the Sapera Grab demo will not crash when the requested number of host frame buffers is not allocated.

The following calculation is an example of the amount of contiguous memory to reserve beyond 5MB with 80,000 buffers of 2048x1024x8:

- a) (80000 \* 64 bytes)

- b) (80000 \* 48 bytes)

- c) (80000 \* (24 + (((2048\*1024)/4kB) \* 8))) = 323MB

- d) Total = a (rounded up to nearest 64kB) + b (rounded up to nearest 64kB) + c (rounded up to nearest 64kB).

#### Host Computer Frame Buffer Memory Limitations

When planning a Sapera application and its host frame buffers used, plus other Sapera memory resources, do not forget the Windows operating system memory needs.

A Sapera application using the preferred *scatter gather buffers* could consume most of the remaining system memory, with a large allocation of frame buffers. If using frame buffers allocated as a *single contiguous memory block*, Windows will limit the allocation dependent on the installed system memory. Use the Buffer menu of the Sapera Grab demo program to allocate host buffer memory until an error message signals the limit allowed by the operating system used.

#### Contiguous Memory for Sapera Messaging

The current value for Sapera messaging determines the total amount of contiguous memory reserved at boot time for messages allocation. This memory space stores arguments when calling a Sapera function. Increase this value if you are using functions with large arguments, such as arrays and experience any memory errors.

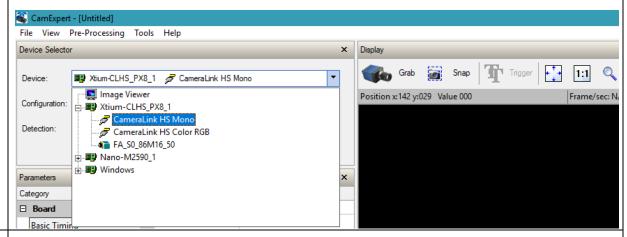

# CamExpert Quick Start

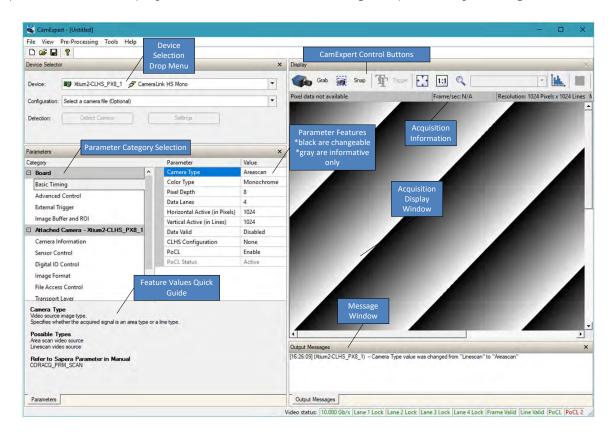

# Interfacing CLHS Cameras with CamExpert

CamExpert is the camera-interfacing tool for Teledyne DALSA frame grabber boards supported by the Sapera library. CamExpert is the primary tool to configure, test and calibrate your camera and imaging setup. Display tools include, image pixel value readout, image zoom, and histogram.

An important component of CamExpert is its live acquisition display window which allows immediate verification of timing or control parameters without the need to run a separate acquisition program.

Functional tools include hardware Flat Field calibration and operation support (see <u>Flat Field Correction</u>: <u>Theory of Operation</u>), plus support for either hardware based or software Bayer filter camera decoding with auto white balance calibration.

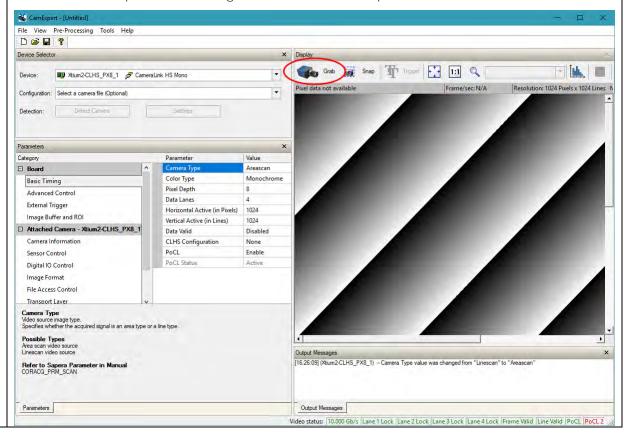

After CamExpert identifies the camera (as per the Camera Link device discovery protocol), timing parameters are displayed and the user can test image acquisition by clicking on *Grab*.

Figure 6: CamExpert Program

CamExpert groups camera features into functional categories. The features shown depend on the frame grabber used and what camera is connected. The values are either the camera defaults or the last stored value when the camera was used. The general descriptions below are not specific to a particular camera.

- Device Selector: Two drop menus allow selection of which device and which saved configuration to use.

- Device: Select which acquisition device to control and configure a camera file. Required in cases where there are multiple boards in a system and when one board supports multiple acquisition types. Note in this example, the installed Xtium2-CLHS PX8 has firmware to support a monochrome or color RGB Camera Link HS camera.

- Configuration: Select the timing for a specific camera model included with the Sapera installation or a standard video standard. The *User's* subsection is where user created camera files are stored.

- Parameter Groups: Select a function category and change parameter values as required. Descriptions for the camera parameters change dependent on the camera.

- Basic Timing: Provides or change static camera parameters.

- Advanced Controls: Advanced parameters used to select various integration methods, frame trigger type, Camera Link HS controls, etc.

- External Trigger: Parameters to configure the external trigger characteristics.

- Image Buffer and ROI: Allows control of the host buffer dimension and format.

- Display: An important component of CamExpert is its live acquisition display window, which allows immediate verification of timing or control parameters without the need to run a separate acquisition program. Grab starts continuous acquisition (button then toggles to Freeze to stop). Snap is a single frame grab. Trigger is a software trigger to emulate an external source.

- Output Messages and Video Status Bar: Events and errors are logged for review. Camera connection status is displayed where green indicates connected signals present.

The CamExpert tool is described more fully in the Sapera Getting started and Sapera Introduction manuals.

# Sapera Camera Configuration Files

CamExpert generates the Sapera camera configuration file (yourcamera.ccf) based on timing and control parameters entered. When using the Sapera LT API in your imaging application, the frame grabber parameter settings can be loaded from this file. For backward compatibility with previous versions of Sapera, CamExpert also reads and writes the \*.cca and \*.cvi camera parameter files.

Every Sapera demo program starts with a dialog window to select a camera configuration file (for details on the included demos, see the Sapera Demo Applications section). Even when using the Xtium-CL MX4 with common video signals, a camera file is required. Therefore, CamExpert is typically the first Sapera application run after an installation. Existing .ccf files can be copied to any new board installations when similar cameras are used.

## Camera Types & Files

The Xtium2-CLHS PX8 supports digital area scan or line scan cameras using the Camera Link HS interface standard. Browse our web site [http://www.teledynedalsa.com/imaging/] for the latest information on Teledyne DALSA Camera Link HS cameras.

#### Camera Files Distributed with Sapera

The Sapera distribution includes camera files for a selection of Xtium2-CLHS PX8 supported cameras. Using the Sapera CamExpert program, you may use the camera files (CCA) provided to generate a camera configuration file (CCF) that describes the desired camera and frame grabber configuration..

Teledyne DALSA continually updates a camera application library composed of application information and prepared camera files. Camera files are ASCII text, readable with Windows Notepad on any computer without having Sapera installed.

# Overview of Sapera Acquisition Parameter Files (\*.ccf or \*.cca/\*.cvi)

#### Concepts and Differences between the Parameter Files

There are two components to the legacy Sapera acquisition parameter file set: CCA files (also called cam-files) and CVI files (also called VIC files, i.e. video input conditioning). The files store video-signal parameters (CCA) and video conditioning parameters (CVI), which in turn simplifies programming the frame-grabber acquisition hardware for the camera in use. Sapera LT 5.0 introduces a new camera configuration file (CCF) that combines the CCA and CVI files into one file.

Typically, a camera application will use a CCF file per camera operating mode (or one CCA file in conjunction with several CVI files, where each CVI file defines a specific camera-operating mode). An application can also have multiple CCA/CCF files to support different image format modes supported by the camera or sensor (such as image binning or variable ROI).

#### CCF File Details

A file using the ".CCF" extension, (Camera Configuration files), is the camera (CCA) and frame grabber (CVI) parameters grouped into one file for easier configuration file management. This is the default Camera Configuration file used with Sapera LT 5.0 and the CamExpert utility.

#### CCA File Details

Teledyne DALSA distributes camera files using the legacy ".CCA" extension, (CAMERA files), which contain all parameters describing the camera video signal characteristics and operation modes (what the camera outputs). The Sapera parameter groups within the file are:

- Video format and pixel definition

- Video resolution (pixel rate, pixels per line, lines per frame)

- Synchronization source and timing

- Channels/Taps configuration

- Supported camera modes and related parameters

- External signal assignment

#### CVI File Details

Legacy files using the ".CVI" extension contain all operating parameters related to the frame grabber board - what the frame grabber can actually do with camera controls or incoming video. The Sapera parameter groups within the file are:

- Activate and set any supported camera control mode or control variable.

- Define the integration mode and duration.

- Define the strobe output control.

- Allocate the frame grabber transfer ROI, the host video buffer size and buffer type (RGB888, RGB101010, MON08, and MON016).

- Configuration of line/frame trigger parameters such as source (internal via the frame grabber /external via some outside event), electrical format (TTL, RS-422, OPTO-isolated), and signal active edge or level characterization.

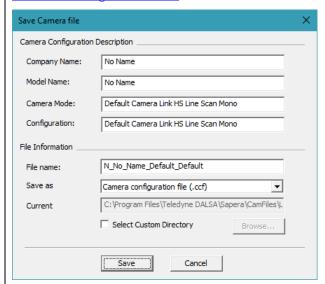

## Saving a Camera File

Use CamExpert to save a camera file (\*.ccf) usable with any Sapera demo program or user application.

When CamExpert is setup as required, click on **File•Save As** to save the new .ccf file. The dialog that opens allows adding details such as camera information, mode of operation, and a file name for the .ccf file.

# Camera Interfacing Check List

Before interfacing a camera from scratch with CamExpert:

- Confirm that Teledyne DALSA has not already published an application note with camera files [ <a href="www.teledynedalsa.com">www.teledynedalsa.com</a> ].

- Confirm that the correct version or board revision of Xtium2-CLHS PX8 is used. Confirm that the required firmware is loaded into the Xtium2-CLHS PX8.

- Confirm that Sapera does not already have a .cca file for your camera installed on your hard disk. If there is a .cca file supplied with Sapera, then use CamExpert to generate the .ccf file with default parameter values matching the frame grabber capabilities.

- Check if the Sapera installation has a similar type of camera file. A similar .cca file can be loaded into CamExpert and modified to match timing and operating parameters for your camera, and lastly save them as Camera Configuration file (.ccf).

- Finally, if there is no file for your camera, run CamExpert after installing Sapera and the acquisition board driver, select the board acquisition server, and manually enter the camera parameters.

# Using CamExpert with Xtium2-CLHS PX8

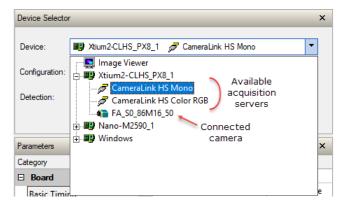

The Sapera CamExpert tool is the interfacing tool for Xtium2-CLHS PX8 frame grabbers and connected cameras; it is supported by the Sapera library and hardware. CamExpert allows a user to test frame grabber and camera functions. Additionally CamExpert saves the frame grabber settings configuration as individual camera parameter files on the host system (\*.ccf).

When an acquisition server is selected, CamExpert only presents parameters supported by the selected device.

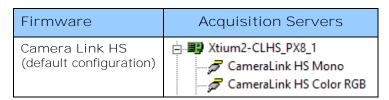

The Xtium2-CLHS PX8 firmware supports one Camera Link HS camera and provides the following acquisition servers:

Depending on the selected server, different parameters may be displayed. For example, with an RGB acquisition server, the Color Type parameter is not displayed since its value is not configurable.

For more information, see the Sapera Servers and Resources section.

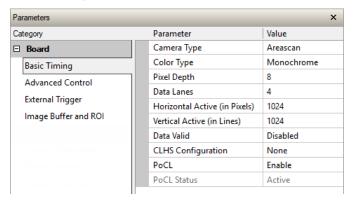

# **Basic Timing Category**

The Basic Timing category groups parameters such as camera type, the active image size, and other settings related to basic timing.

## Parameter Descriptions

The following table describes the CamExpert Basic Timing category of Sapera LT parameters. Acquisition server notes, if applicable, indicate if parameter availablility or supported values are dependent on the selected frame grabber acquisition server and acquisition device.

| Display Name                  | Parameter                     | Description                                                                                                                                           | Notes                                                        |

|-------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Camera Type                   | CORACO PRM SCAN               | Video source image type. Possible values are areascan or line scan.                                                                                   | Not shown for Bayer<br>servers (areascan<br>only).           |

| Color Type                    | CORACO PRM VIDEO              | Sets the color format of the input source.                                                                                                            | Not shown for RGB servers.                                   |

|                               |                               |                                                                                                                                                       | Monochrome servers<br>support:<br>Monochrome<br>Bayer mosaic |

| Pixel Depth                   | CORACO_PRM_PIXEL_DEPTH        | Pixel depth (bits per pixel) of the input source.                                                                                                     | Not shown for RGB servers.                                   |

|                               |                               |                                                                                                                                                       | Monochrome servers<br>support:<br>8, 10, 12, 14 or 16 bit    |

| Data Lanes                    | CORACO PRM DATA LANES         | Number of data lanes output by the camera.                                                                                                            |                                                              |

| Horizontal Active (in Pixels) | CORACO_PRM_HACTIVE            | Sets the horizontal camera resolution in pixels. This corresponds to the visible part of the image from the camera.                                   |                                                              |

|                               |                               | Valid range is:                                                                                                                                       |                                                              |

|                               |                               | min = 32 pixel<br>max = 65536 pixel<br>step = 32 pixel                                                                                                |                                                              |

|                               |                               | Note: minimum is per lane                                                                                                                             |                                                              |

| Vertical Active (in Lines)    | CORACO PRM VACTIVE            | Sets the vertical camera resolution in lines per frame. This corresponds to the visible part of the image from the camera. Valid range is 1-16777215. | Not shown for linescan cameras.                              |

| Data Valid                    | CORACO_PRM_DATA_VALID_ENABLE  | Specifies if the acquisition board uses the camera data valid signal. Boolean parameter (TRUE or FALSE).                                              |                                                              |

| CLHS Configuration            | CORACQ_PRM_CLHS_CONFIGURATION | Sets the board's CLHS configuration. Possible values are:                                                                                             |                                                              |

|                               |                               | • None                                                                                                                                                |                                                              |

|                               |                               | Manual Acquisition Start/Stop                                                                                                                         |                                                              |

| PoCL        | CORACO_PRM_POCL_ENABLE   | Enables/disables sending power through the Camera Link CLHS cable for Active Optical Cable (AOC). Boolean parameter (TRUE or FALSE). |  |

|-------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| PoCL Status | CORACO PRM SIGNAL STATUS | Status of power signals connected to the acquisition device. Possible values are Active or Not Active.                               |  |

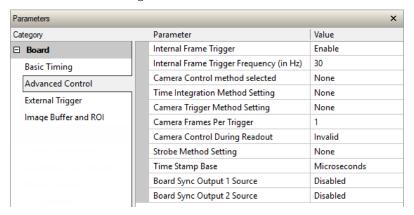

# **Advanced Control Category**

The Advanced Control category groups parameters for configuring camera control signals, board sync outputs and other advanced settings.

# Parameter Descriptions

The following table describes the CamExpert Advanced Control category of Sapera LT parameters. Acquisition server notes, if applicable, indicate if parameter availablility or supported values are dependent on the selected frame grabber acquisition server and acquisition device.

| Display<br>Name                                 | Parameter                                                                                                   | Description                                                                                                                                                           | Notes                             |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Internal Frame<br>Trigger                       | CORACO_PRM_INT_FRAME_TRIGGER_ENABLE                                                                         | Enables/disables the acquisition device's internal frame trigger. Boolean parameter (TRUE or FALSE).                                                                  | Applies to areascan cameras only. |

| Internal Frame<br>Trigger Frequency<br>(in Hz)  | CORACQ_PRM_INT_FRAME_TRIGGER_FREQ                                                                           | Internal frame trigger frequency in Hz. Set to the required frame rate when using internal frame trigger to control camera acquisition. Valid range is 0.001-10000Hz. |                                   |

| Line Sync Source                                | CORACO PRM EXT LINE TRIGGER ENABLE<br>CORACO PRM INT LINE TRIGGER ENABLE<br>CORACO PRM SHAFT ENCODER ENABLE | Selects the line trigger source for linescan cameras, unless free-running.                                                                                            | Applies to linescan cameras only. |

| Interal Line<br>Trigger Frequency<br>(in Hz)    | CORACO_PRM_INT_LINE_TRIGGER_FREO                                                                            | Sets the internal line trigger frequency, in Hz. Applies only when the Line Sync Source is set to Internal Line Trigger.                                              | Applies to linescan cameras only. |

| Camera Line<br>Trigger Frequency<br>Min (in Hz) | CORACO_PRM_CAM_LINE_TRIGGER_FREO_MIN                                                                        | Sets the camera's minimum line trigger frequency. Minimum value is 1Hz.                                                                                               | Applies to linescan cameras only. |